編碼器_傳感器_讀碼器_機(jī)器視覺 - 西安德伍拓自動化傳動系統(tǒng)有限公司

- 行業(yè)解決方案?。?a href="/company/lianxi.html" >聯(lián)系我們

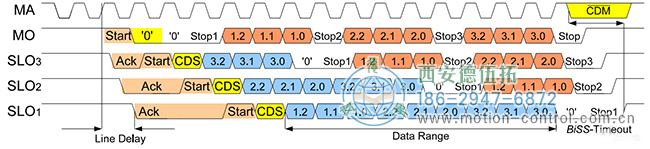

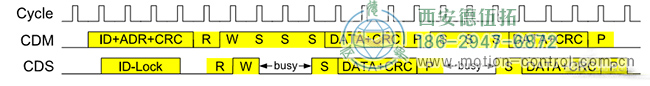

圖8:BiSS通信幀實例

在線QQ

在線QQ 186-2947-6872

186-2947-6872 在線咨詢

在線咨詢

掃描二維碼

添加客服微信號

info@motion-control.com.cn

info@motion-control.com.cn